内部 IP 的使用

1.)PLL

AGRV2K 器件支持 1 个 PLL。若需用到 PLL,可以直接在 Quartus II 工程中添加 MegaWizard IP

(ALTPLL)。PLL 时钟输入要用 IO_GB 管脚。

2.)RAM

AGRV2K 器件支持 4 个 M9K Block(1K Byte),共 4K Byte 空间。可直接在 Quartus II 工程中

MegaWizard 中添加 Memory IP。不要超过 4 个 M9K。

3.)内部晶振

AGRV2K 器件内部有一 8MHz 晶振,可作为逻辑设计的时钟输入,也可接入 PLL,并支持精

度自校准。

设计中使用这个晶振的时钟输入,需要在 ve 文件中指定时钟输入管脚位置为 PIN_OSC,如:

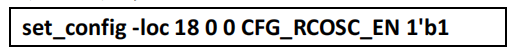

并在设置文件 led.asf 中加入语句:

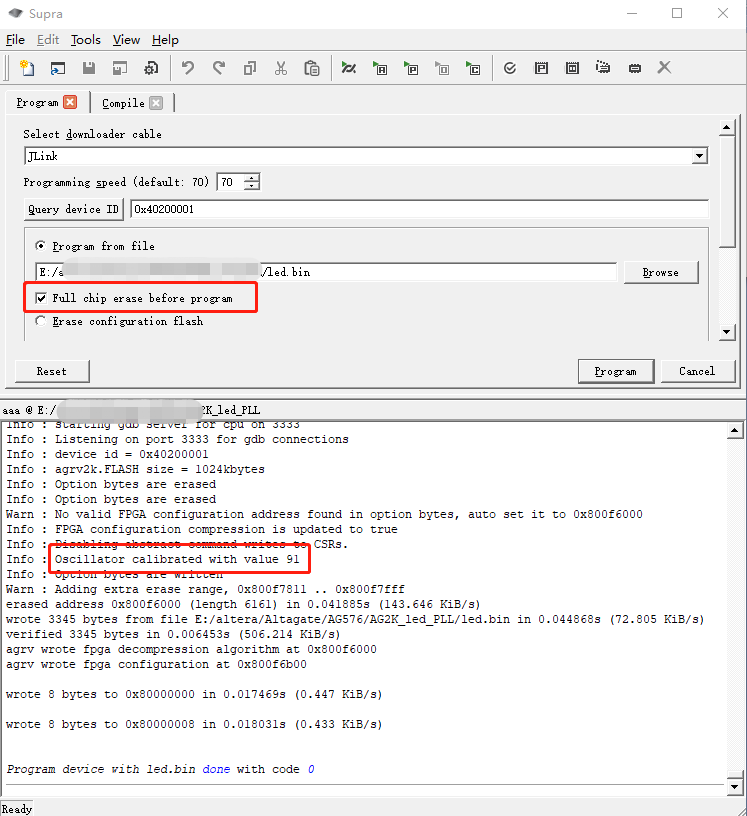

工程编译完成后,烧录界面,Program 需选择“Full chip erase before program”。

Program 后显示的信息中包含“Info : Oscillator calibrated with value xx”即表示内部晶振已打

开并校准,可以正常使用。

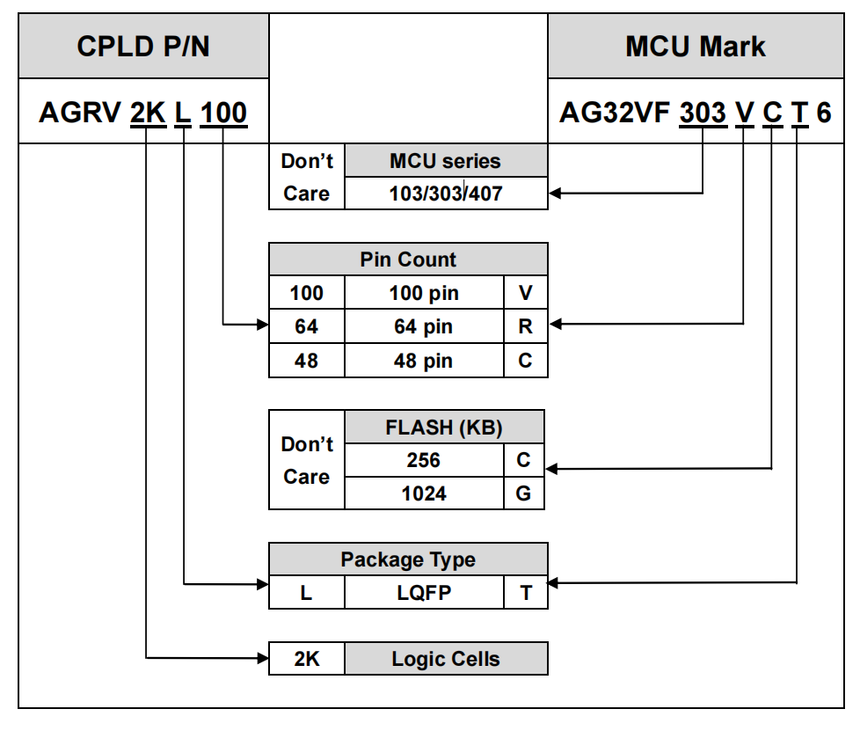

型号说明

AGRV2K 为 AGM 软件中的型号,实际是 AG32 MCU 系列芯片中的逻辑部分。所以芯片封装

丝印为 AG32 MCU 的 AG32VF 系列型号。选型时只需参考 MCU 型号的对应封装,即可作为

CPLD 使用。

需要获取更多的资料和支持可以联系我们

提供“芯片测样-发送资料-技术支持-批量采购”

联系方式: 姚经理 13661545024(VX同号)

(加的时候备注下公司名和个人名字)

在线商城:agm-micro.taobao.com

公司网站:www.agm-micro.com