时间:2024-03-03作者:CSDN:平日光辉【转载】

一、软件安装

此次用到的软件如下图所示:Quartus、Supra

Supra下载——

链接:https://pan.baidu.com/s/1eVXGb10pj_GHZhK-m2ZF6w?pwd=1234

提取码:1234

(下载最新版)

二、生成项目

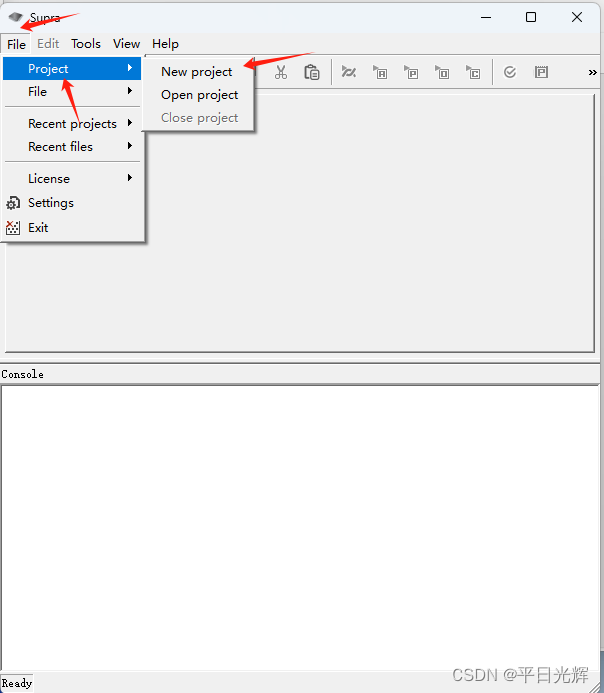

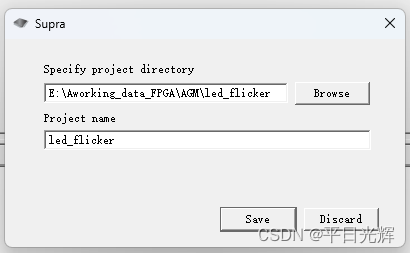

1、打开刚刚安装好的Supra:File-Pro-New Pro新建工程

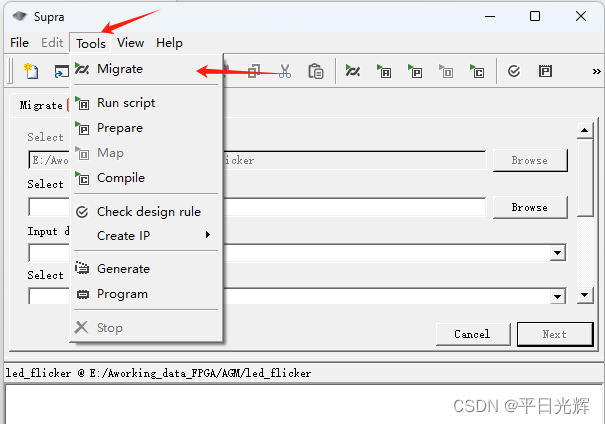

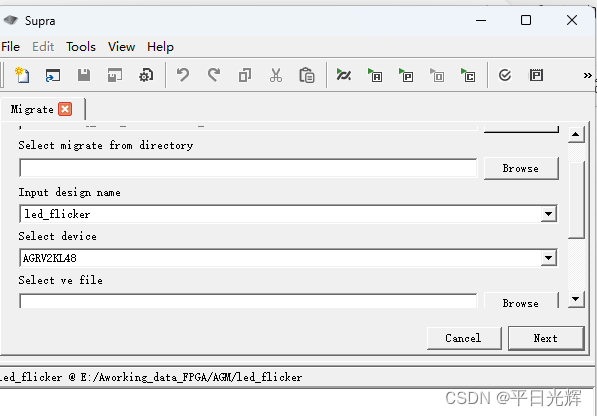

2、Tools-Migrate输入设计信息

我这里输入设计名称、芯片型号AGRV2KL48

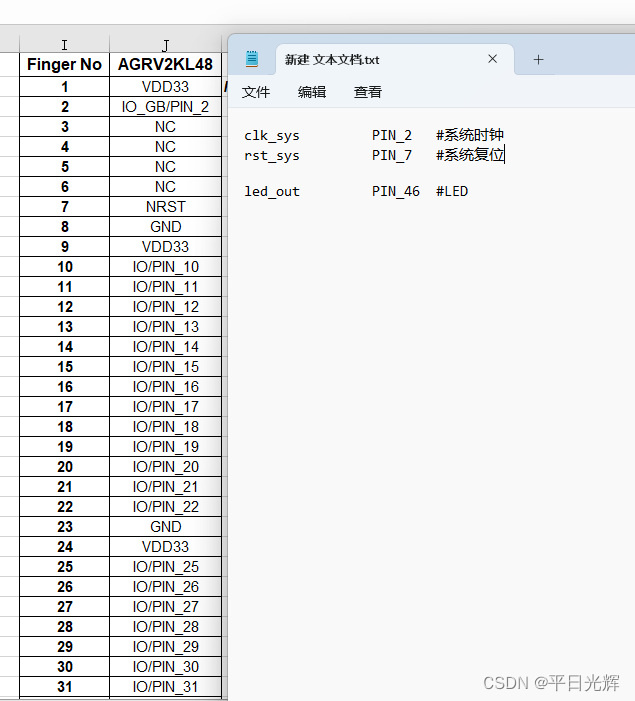

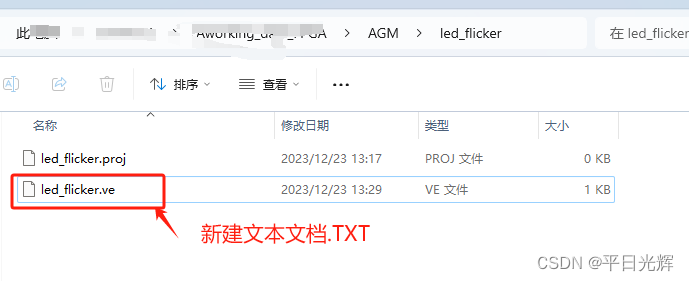

接下来需要选择一个ve文件,这个ve文件为IO的管脚位置设置文件,这个文件可以用txt“新建文本”编辑后更改为ve文件即可,如下:

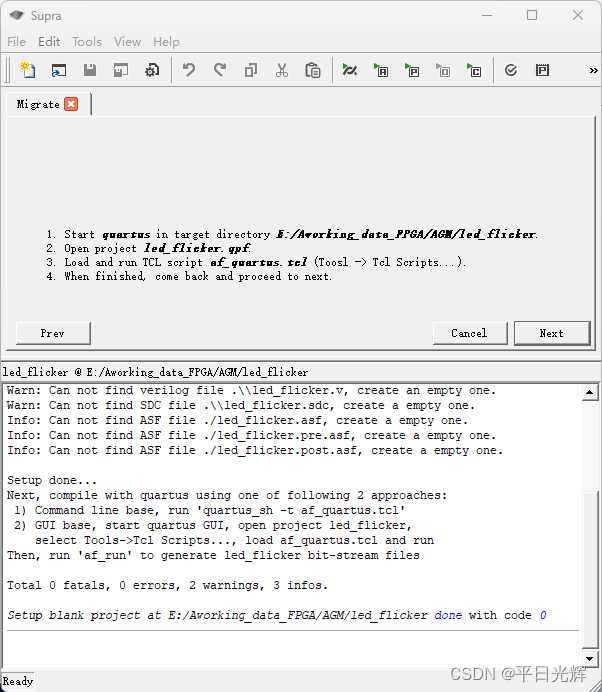

3、设计生成next

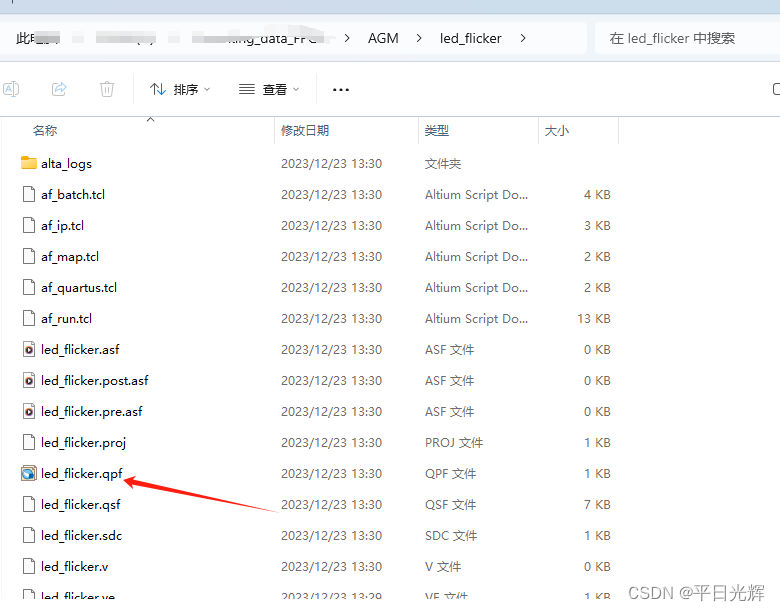

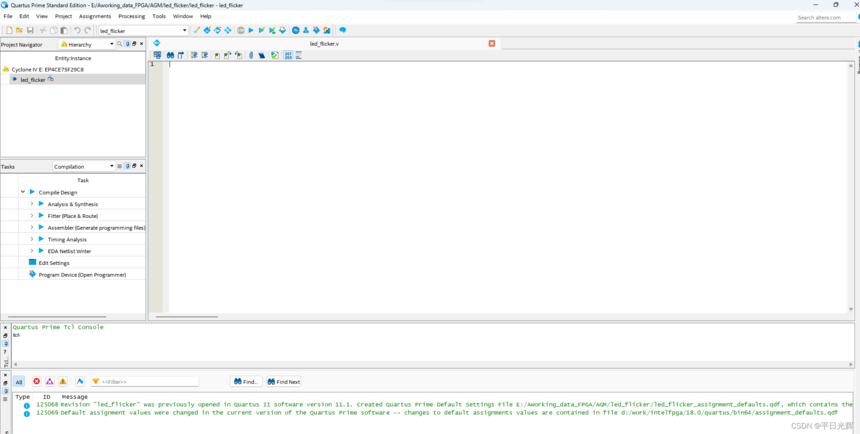

4、Quartus打开工程并设计

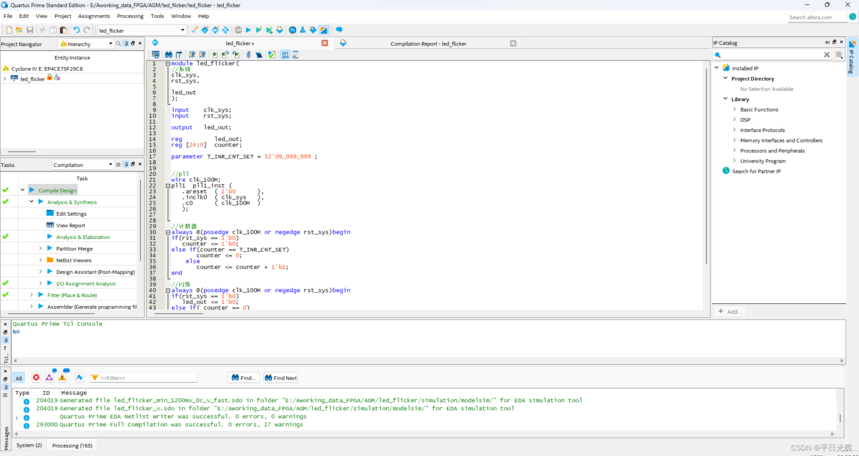

写入逻辑

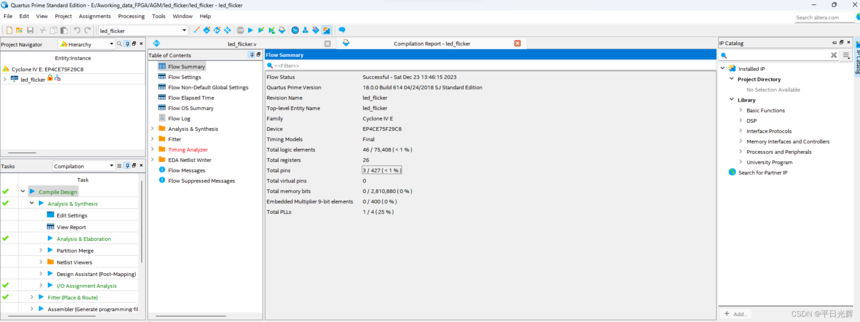

编译成功后其逻辑数不能超过2K

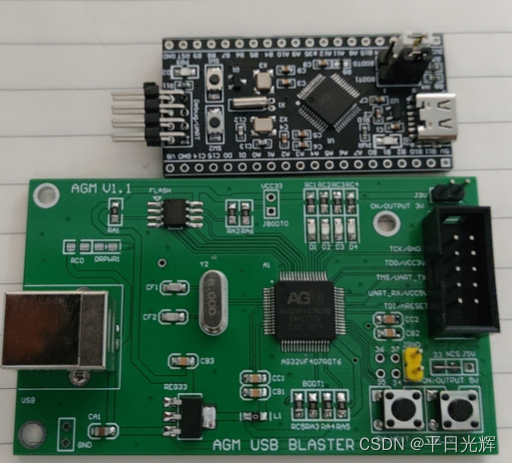

代码中用到了PLL的ip核,AGM的该型号支持PLLIP,其中关于pll的输入时钟,即系统时钟解释如下:(该款FPGA用了双晶振8M无源和50M有源,50M是纯cpld使用,8M无源是给内部纯mcu使用,其中PIN2引脚默认50MHz有源,这也是该芯片的一个优势)

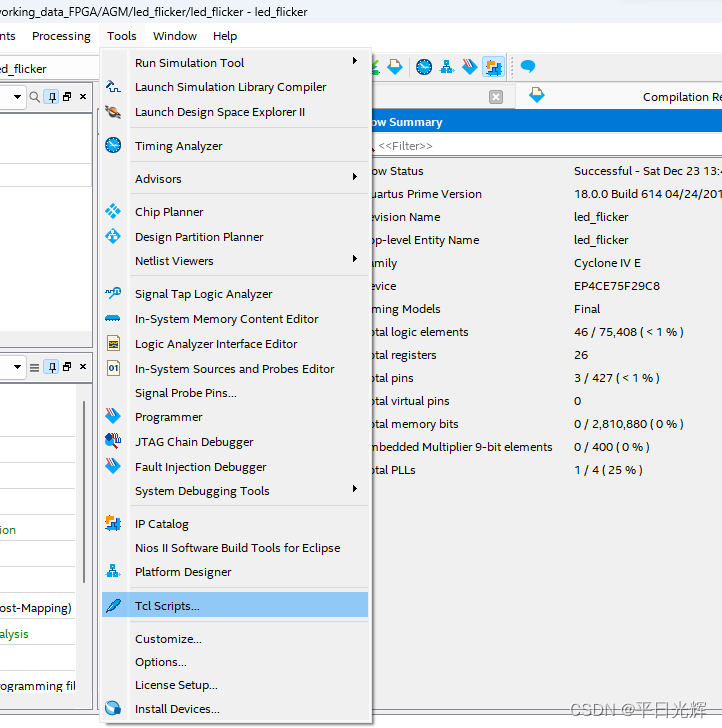

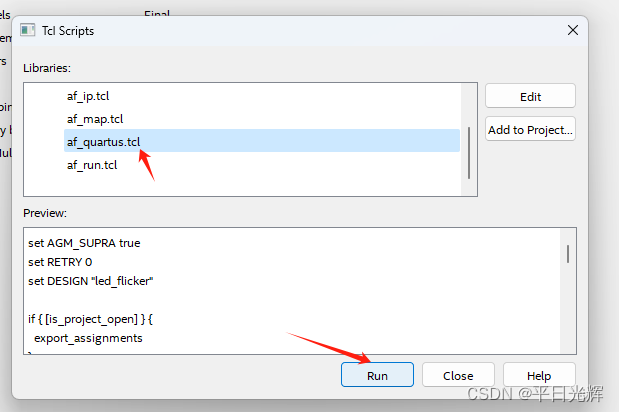

Tools-Tcl生成vo文件

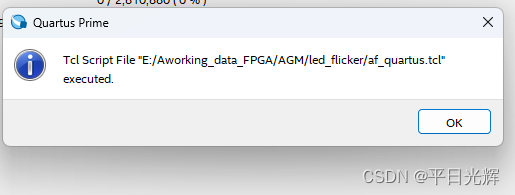

选择af_quartus-run

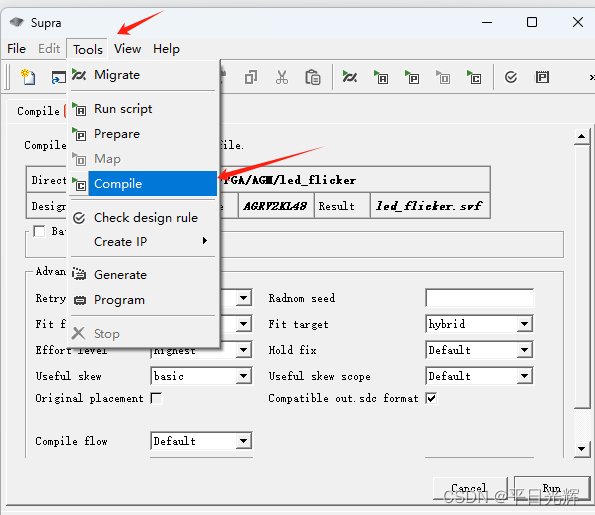

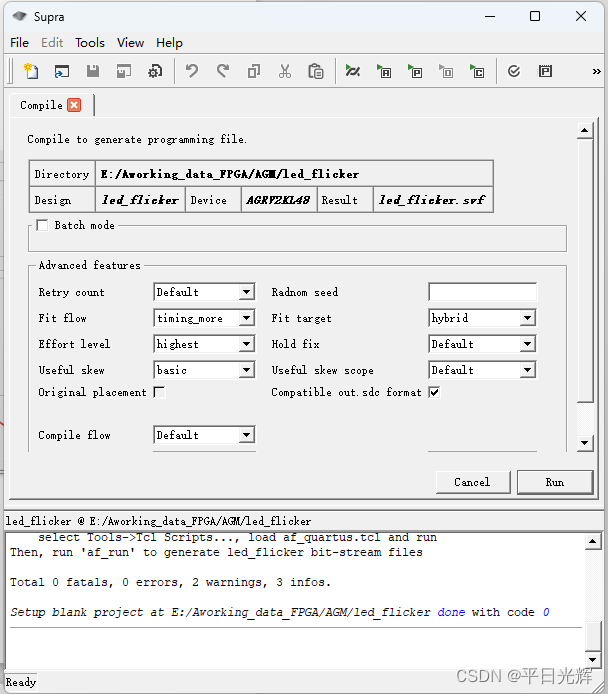

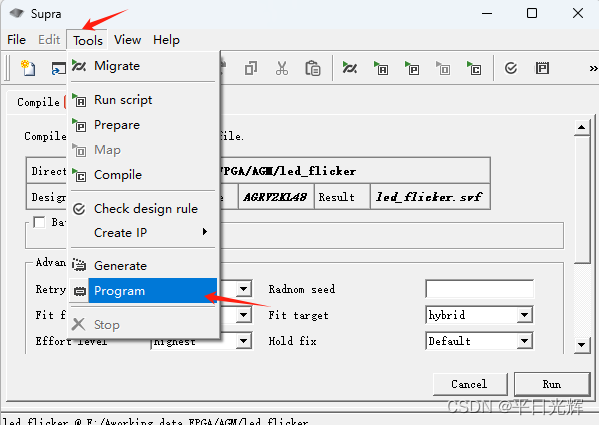

转到Supra生成bin文件Tools-Com

点击:run

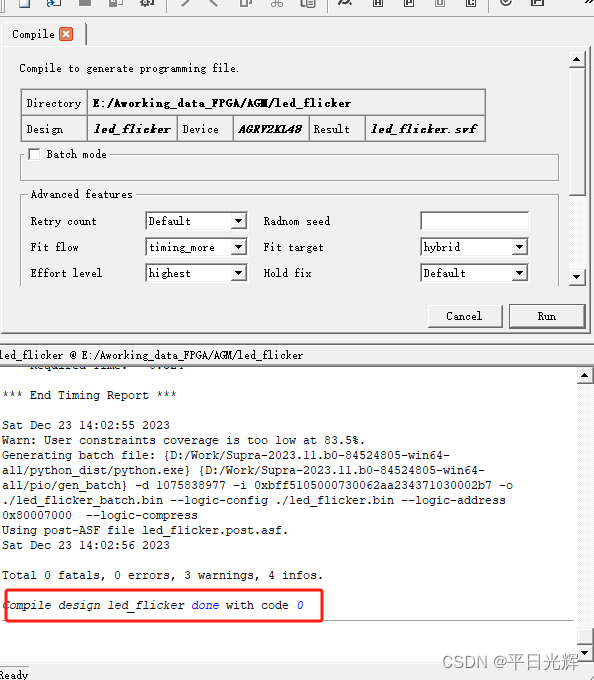

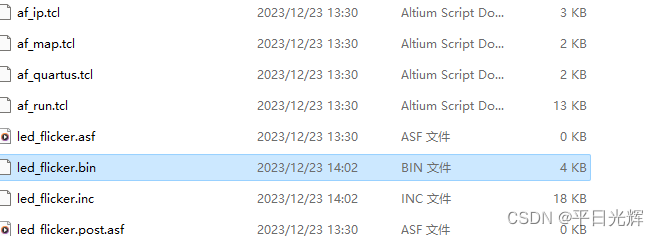

bin生成成功

三、下载

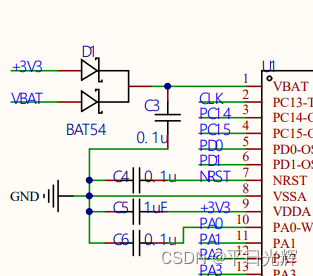

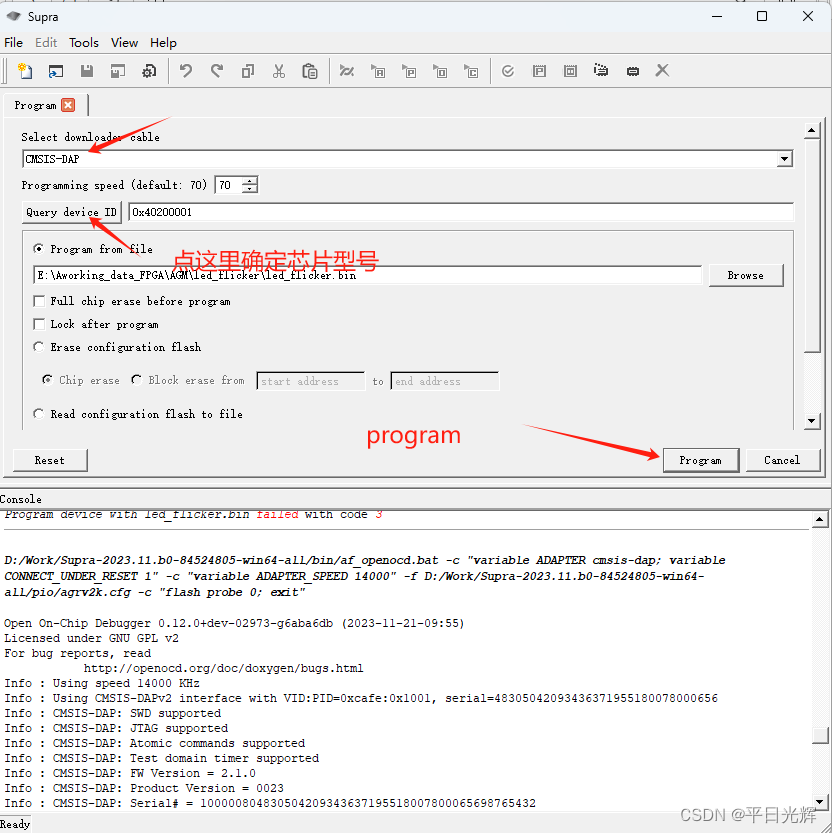

硬件连接(GND、TCK、TMS)

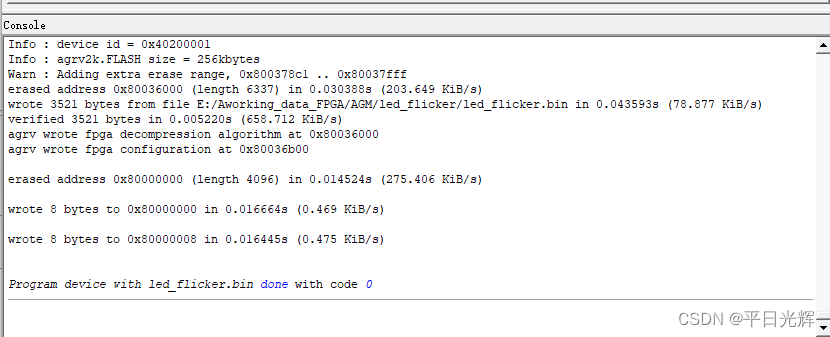

烧录方式选择CMSIS-DAP,Query device ID,program

成功

提供一个DEMO供参考:

需要获取更多的“资料”和“支持”和“样片测样申请”可以联系我们

提供“芯片测样-发送资料-技术支持-批量采购”

联系方式: 姚经理 13661545024(VX同号)

(加的时候备注下公司名和个人名字)

在线商城:agm-micro.taobao.com

公司网站:www.agm-micro.com