AG16KL144H 如何升级使用 16K LEs

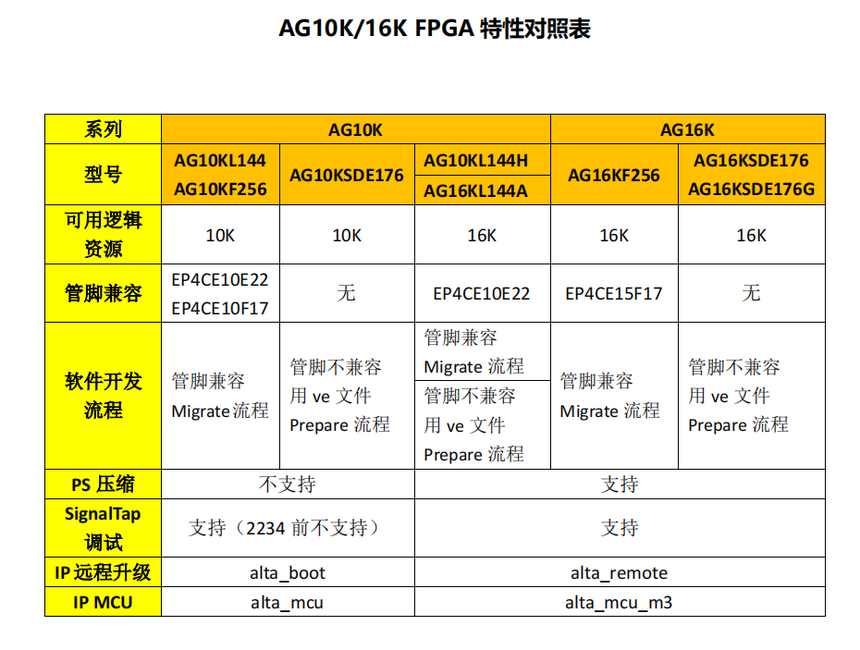

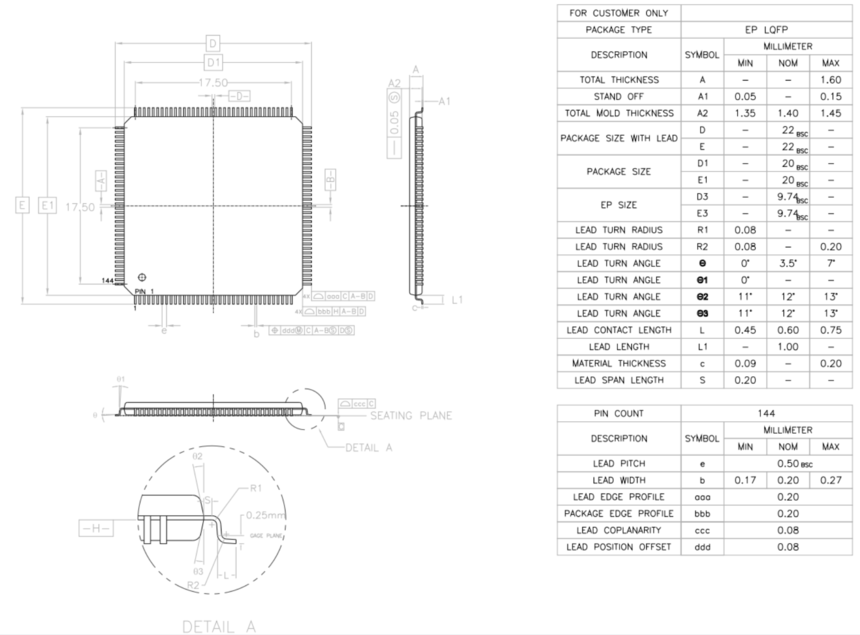

AG16KL144A 为 AG10KL144 管脚兼容型号,但实际逻辑资源可以达到 16K LEs,也可使

用 AG16K IP。如果仅用 10K,可以遵循原兼容型号设计转换流程(参考 Manual_supra.pdf),

即采用 Quartus 的 EP4CE10E22 工程来转换,只是 Supra 内型号选择 AG10KL144H。

如果希望用到 16K LEs,需要采用非兼容型号的 prepare 设计流程,类似 AG10K/16K

SDE176 系列。Supra 里选择 AG16KL144A 这个新型号。

软件开发流程(Compatible 模式)

先用 Quartus 基于 Cyclone IV EP4CE15F23 为基础完成原始设计。管脚位置分配可先清空。

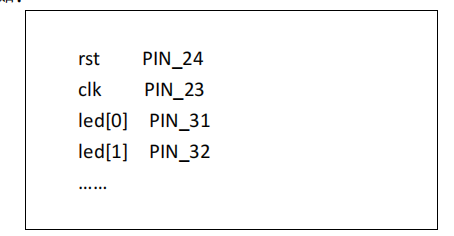

新建一个文本格式的管脚分配文件,命名为<design>.ve。编辑 ve 文件加入 FPGA 的 IO

位置设置,这里需要参考 AG10KL144 的管脚位置,ve 文件格式如下(管脚设计名称+空格+

封装管脚名称),例如:

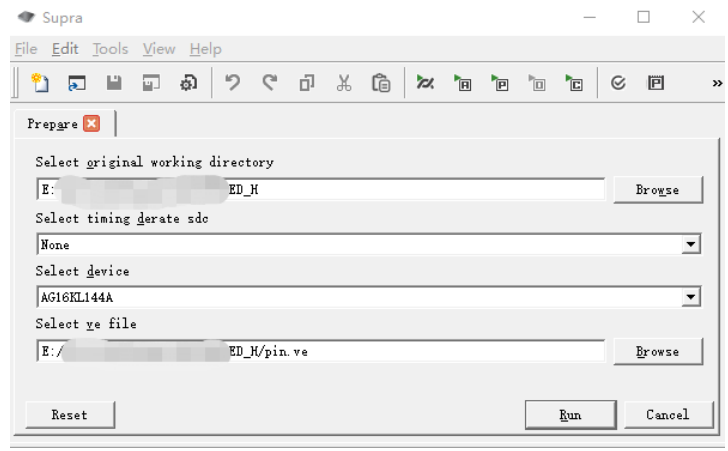

新建一空目录作为 AG16KL144A 的项目目录。打开 AGM Supra 软件,在此目录中新建工

程。执行 Tools-Prepare。选择原 Quartus II 项目目录,Device 选 AG16KL144A,并选择编辑好

的 ve 文件后,点击 Run。正确运行后会生成 af_prepare.tcl 等文件。

打开原 Quartus 项目,通过 Tools-Tcl Scripts 运行 af_prepare.tcl 脚本文件,会把 ve 的内

容导入到 EP4CE15 对应的管脚分配,并继续执行编译过程,在项目目录中生成 Simulation 目

录以及综合后的 vo 等文件。

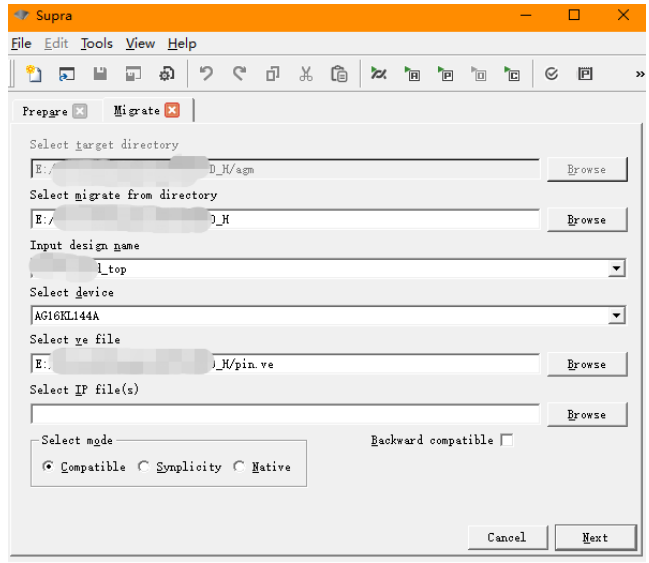

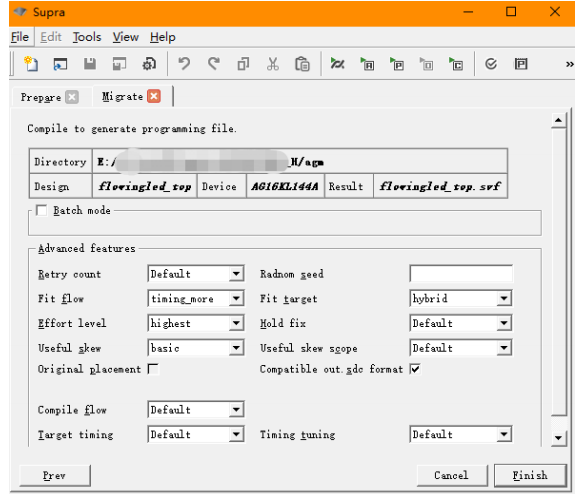

打开 AGM Supra 软件,执行 Tools-Migrate。Target directory 默认为当前工程目录,From

directory 为原 EP4CE15 的工程目录。Input design name,可以从下拉框中直接选取。Device

为 AG16KL144A,同样选择 ve 文件。

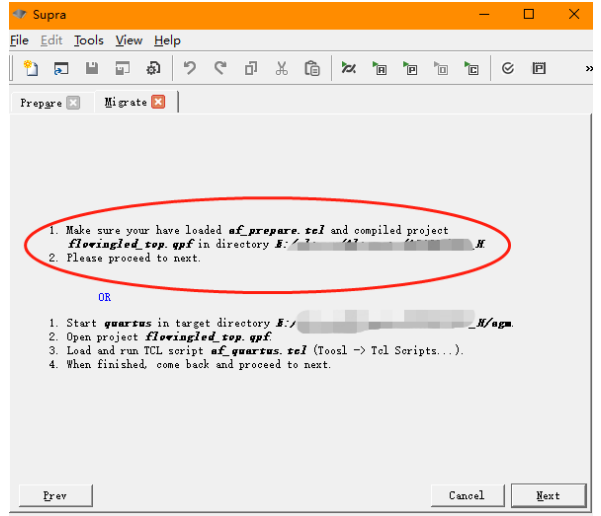

点击 Next,参考页面说明 OR 上面的部分(确认前面已运行过 af_prepare.tcl)即直接点

击 Next。

下面进入编译界面中,可设置编译参数,或直接采用默认设置。

点击 Finish,进入编译过程,在 Console 窗口可查看编译信息 log。成功编译后,即生成

配置烧写文件。

提示:如需继续修改原设计代码(不改变管脚),由于 af_prepare.tcl 已把管脚设置好,

可直接在原 Quartus 工程中修改代码并完全编译。然后在 Supra 中执行 Tools-Compile,即上

面最后一步界面,点击 Run 完成最终编译。

需要获取更多的“资料”和“支持”和“样片测样申请”可以联系我们

提供“芯片测样-发送资料-技术支持-批量采购”

联系方式: 姚经理 13661545024(VX同号)

(加的时候备注下公司名和个人名字)

在线商城:agm-micro.taobao.com

公司网站:www.agm-micro.com